|

| | PermutedViewConstExpr (const Tensor &t) noexcept |

| |

| | PermutedViewConstExpr (const PermutedViewConstExpr &)=delete |

| |

| PermutedViewConstExpr & | operator= (const PermutedViewConstExpr &)=delete |

| |

| | PermutedViewConstExpr (PermutedViewConstExpr &&)=delete |

| |

| PermutedViewConstExpr & | operator= (PermutedViewConstExpr &&)=delete |

| |

| template<typename Output > |

| bool | may_alias (const Output &output) const noexcept |

| |

template<typename... Indices>

requires (sizeof...(Indices) == NumDims) |

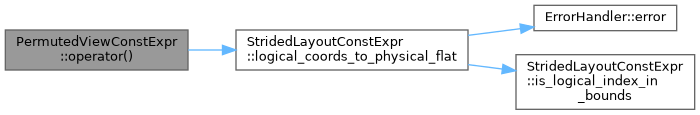

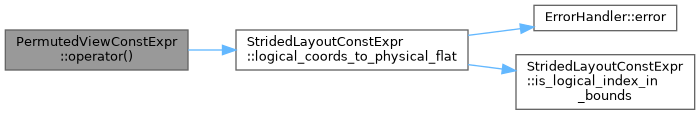

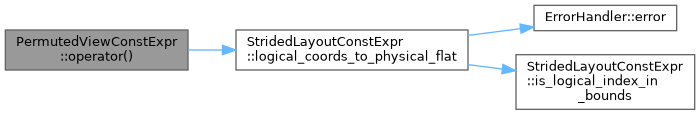

| FORCE_INLINE const value_type & | operator() (Indices... indices) const TESSERACT_CONDITIONAL_NOEXCEPT |

| |

| FORCE_INLINE const value_type & | operator() (my_size_t(&indices)[NumDims]) const TESSERACT_CONDITIONAL_NOEXCEPT |

| |

| FORCE_INLINE const value_type & | operator() (const my_size_t *indices) const TESSERACT_CONDITIONAL_NOEXCEPT |

| |

| template<typename T , my_size_t Bits, typename Arch > |

| FORCE_INLINE Microkernel< T, Bits, Arch >::VecType | evalu (my_size_t logical_flat) const noexcept |

| | SIMD EVALUATION — logical flat, K::gather.

|

| |

| template<typename T , my_size_t Bits, typename Arch > |

| FORCE_INLINE Microkernel< T, Bits, Arch >::VecType | logical_evalu (my_size_t logical_flat) const noexcept |

| |

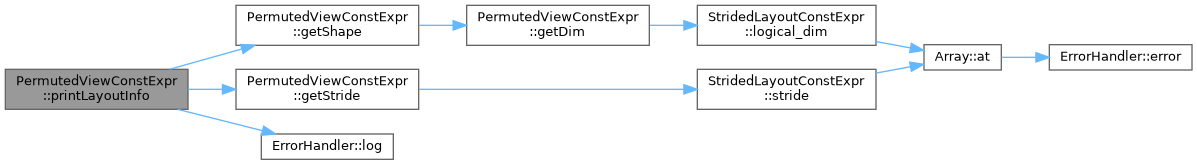

| void | printLayoutInfo () const |

| |

| FORCE_INLINE const Tensor & | transpose () const noexcept |

| |

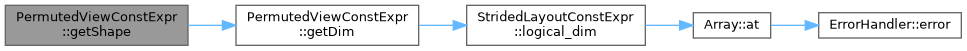

| std::string | getShape () const |

| |

| FORCE_INLINE constexpr const value_type * | data () const noexcept |

| |

| FORCE_INLINE constexpr value_type * | data () noexcept |

| |

| const PermutedViewConstExpr< Tensor, Perm... > & | derived () const |

| |

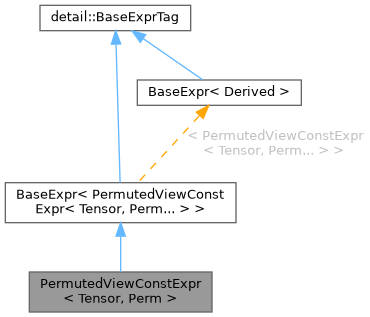

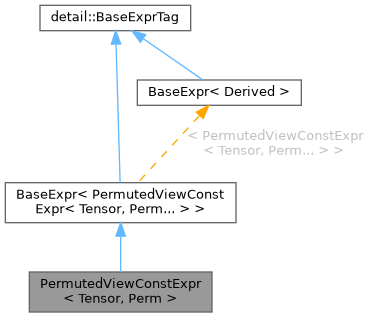

template<typename Tensor, my_size_t... Perm>

class PermutedViewConstExpr< Tensor, Perm >

Compile-time permuted view over a tensor.

Does not own or copy data — references the underlying tensor's physical buffer. Permutation is applied entirely at compile time through StridedLayoutConstExpr.

The permuted layout reinterprets the same physical memory with permuted logical dimensions and strides:

Source A[2,3] padded to [2,4]: Physical: [a b c 0 | d e f 0] Layout: LogicalDims=[2,3], Strides=[4,1]

Transposed view (Perm = 1,0): Same physical buffer Layout: LogicalDims=[3,2], Strides=[1,4]

view(0,0) → 0*1 + 0*4 = offset 0 → 'a' view(0,1) → 0*1 + 1*4 = offset 4 → 'd' view(1,0) → 1*1 + 0*4 = offset 1 → 'b' view(2,1) → 2*1 + 1*4 = offset 6 → 'f'

- Template Parameters

-

| Tensor | The underlying tensor type (e.g., FusedTensorND<double, 2, 3>) |

| Perm | Compile-time permutation indices |

template<typename Tensor , my_size_t... Perm>

template<typename T ,

my_size_t Bits, typename Arch >

SIMD EVALUATION — logical flat, K::gather.

Consecutive logical flat indices map to non-contiguous physical offsets through the permuted layout, so gather is required.

Example: transposed [3,2] view of [2,3] source: logical_flat 0 → coords(0,0) → physical 0 logical_flat 1 → coords(0,1) → physical 4 logical_flat 2 → coords(1,0) → physical 1 logical_flat 3 → coords(1,1) → physical 5 → gather from offsets [0, 4, 1, 5]

- Template Parameters

-

| T | The value type for evaluation (e.g., float, double) |

| Bits | Number of bits for the microkernel (e.g., 256 for AVX2) |

| Arch | The target architecture for the microkernel (e.g., AVX2, AVX-512) |

- Parameters

-

| logical_flat | The logical flat index to evaluate from |

- Returns

- Microkernel vector type containing the evaluated values for the SIMD width

Public Member Functions inherited from BaseExpr< PermutedViewConstExpr< Tensor, Perm... > >

Public Member Functions inherited from BaseExpr< PermutedViewConstExpr< Tensor, Perm... > >